OMI AI PLATFORM

Remember Every Moment,

Talk to AI and Get Feedback

Join the #1 open-source AI wearable community

Build faster and better with 3900+ community members on Omi Discord

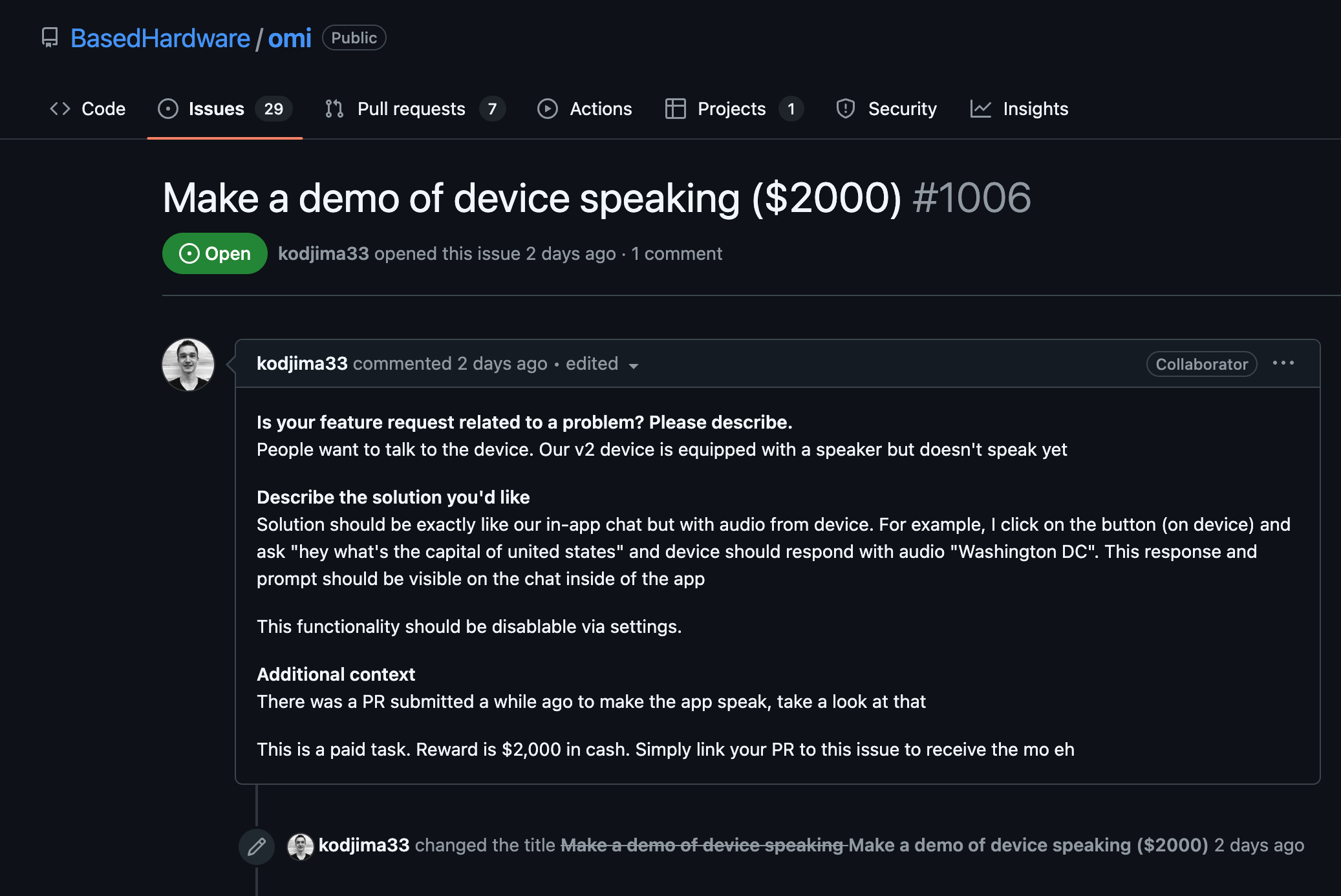

Participate in hackathons to expand the Omi platform and win prizes

Participate in hackathons to expand the Omi platform and win prizes

Get cash bounties, free Omi devices and priority access by taking part in community activities

OMI NECKLACE + OMI APP

First & only open-source AI wearable platform

Omi Dev Kit 2

Product not found

Omi Dev Kit 2: build at a new level

Key Specs

What people say

OMI NECKLACE: DEV KIT

Take your brain to the next level

Product not found