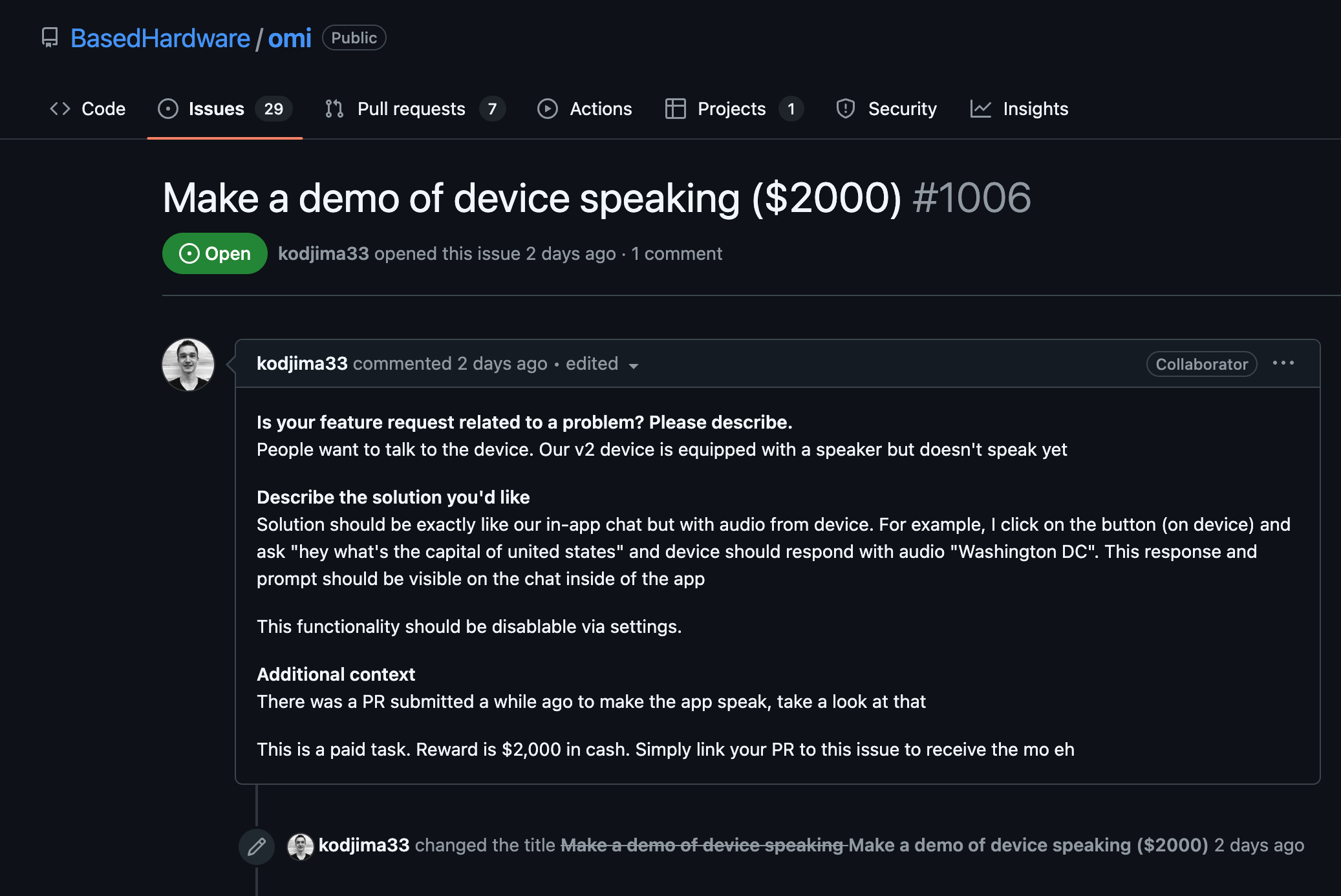

Understanding the Synchronization Issue

Synchronization issues between a Saleae Logic Analyzer and embedded devices primarily arise due to clock skew, signal integrity problems, or misaligned data streams. Addressing these requires a comprehensive understanding of the signal configuration and timing-related constraints in both the logic analyzer and the embedded system.

Troubleshooting Communication Protocols

Review Signal Integrity: Ensure that the signals captured by the logic analyzer have clean edges with minimal noise. Use ground clips effectively and check for reflections or crosstalk in the setup.

Verify Clock and Data Alignment: If using protocols like SPI, I2C, or UART, confirm the clock and data lines are properly aligned. A desynchronization often results from incorrect initial configurations.

Timing Adjustments: Consider using the Saleae software’s timing adjustment feature to set the correct timing for your protocol under test. Adjusting the sample rate and buffer size might also help capture signals more accurately.

Configuring the Logic Analyzer Software

Sample Rate Configuration: The Saleae Logic software allows you to set a high sample rate (at least 4x the fastest signal of interest) to improve the temporal resolution of the collected data, this is crucial to detect fast transitions and edge cases.

Filter Noise: Implement filters within the Saleae software to minimize noise if high-frequency noise is causing synchronization problems. Utilize software-based thresholds to clean recorded data.

Code-Level Synchronization Considerations

To resolve synchronization issues programmatically, ensure that your embedded code configures communication correctly:

// Configure SPI communication

void configureSPI() {

SPI.begin();

// Set SPI Clock to match the Saleae Logic capture

SPI.setClockDivider(SPI_CLOCK_DIV4); // Adjust as needed

SPI.setDataMode(SPI_MODE0); // Ensure Data Mode matches the settings

}

Use of Handshaking Protocols: Implement handshaking mechanisms such as acknowledgments (ACK) and negative acknowledgements (NACK) to ensure both the Saleae and device are synchronized on the data exchange.

Synchronize Overrun Handling: If the device provides a mechanism to detect buffer overruns or underruns, be sure to handle these gracefully in your firmware to ensure data integrity is maintained.

Advanced Techniques

Edge Triggering: Utilize edge-triggering features in your protocol to synchronize actions with specific signal conditions. Employ Saleae’s trigger settings for precise captures.

Time-Correlated Event Logging: In your firmware, log timestamps corresponding to critical events. This is especially useful when comparing against logic analyzer captures for identifying discrepancies.

Testing and Validation

Cross-verification: Validate your synchronization by comparing the data output and the captured Saleae traces. Look for any timing discrepancies and adjust settings accordingly.

Continuous Monitoring: Employ the Saleae analyzer in a continuous monitoring fashion to capture rare or intermittent synchronization issues which might indicate sporadic glitches or jitter.

By carefully analyzing signal integrity, adjusting both the logic analyzer and firmware settings, and utilizing advanced Saleae software features, you can resolve synchronization issues more effectively and ensure reliable data communication.